We quote the special characters in curly braces. But we can’t just use this for the name since TCL will try to call a function 0 rather than using the literal characters. The actual port name for the LSB of the led is led. For the PACKAGE_PIN attribute, we need to be more selective. The set_property command can apply the same IOSTANDARD attribute to all eight.

The call will just return a list of eight ports that match the name led. So we can still use the same IO_STANDARD commands. The square brackets tell TCL to call the function inside them and use the value of the result in place of the brackets.

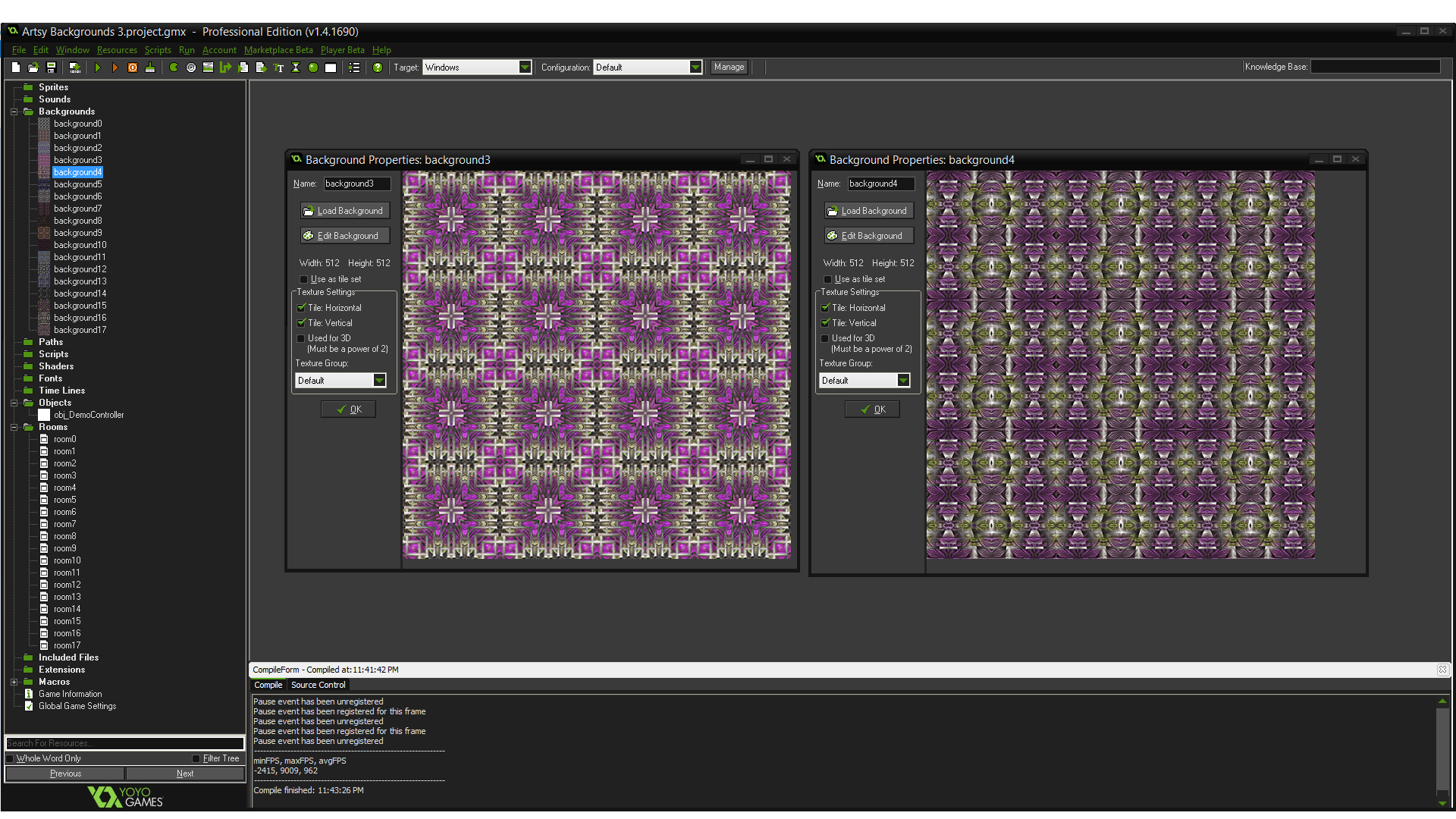

get_ports is another function which searches the design database for ports. set_property is a function defined in TCL, and the values passed to it are arguments. Our constraint files are actually a little program written in the TCL programming language. We need to apply the PACKAGE_PIN to individual pins. However, the constraints do change a fair amount.īefore, the name of the input pin was switch, and the output pin was called led. The width of the values just changes from one bit to eight bits. You don’t need to modify the assignment statement. This will change the inputs and outputs to eight-bit busses. since we have eight of those on our board. So now let’s modify our design to use a bus of eight wires for the switches and LEDs. Congratulations: you have just created a very expensive and complicated wire! More Wires If the blue LED comes on after programming everything should have worked. Generate a bit file and program the board. You should now be able to compile the design. These constraints tell the compiler where we want to connect our inputs and outputs and what logic levels to use for those pins. Edit your top.xdc file so that it contains the following constraints. This is on a 3.3V bank connected to pin T22. If you look at the upper left of the schematic you will see a signal called LD0 which is connected to LED 0. Assuming your jumper is set to 2.5V, that means this is a 2.5V input. This voltage is adjustable on the board between 2.5 and 1.8 volts. Notice also that the voltage on the IO bank where the input belongs (bank 35) is VADJ. Switch 0 comes into the FPGA as SW0 on the schematic and it connects to pin F22 on the FPGA. If you look at the schematic, you’ll see that there are eight switches and eight LEDs. But even so, I have included the important information here.

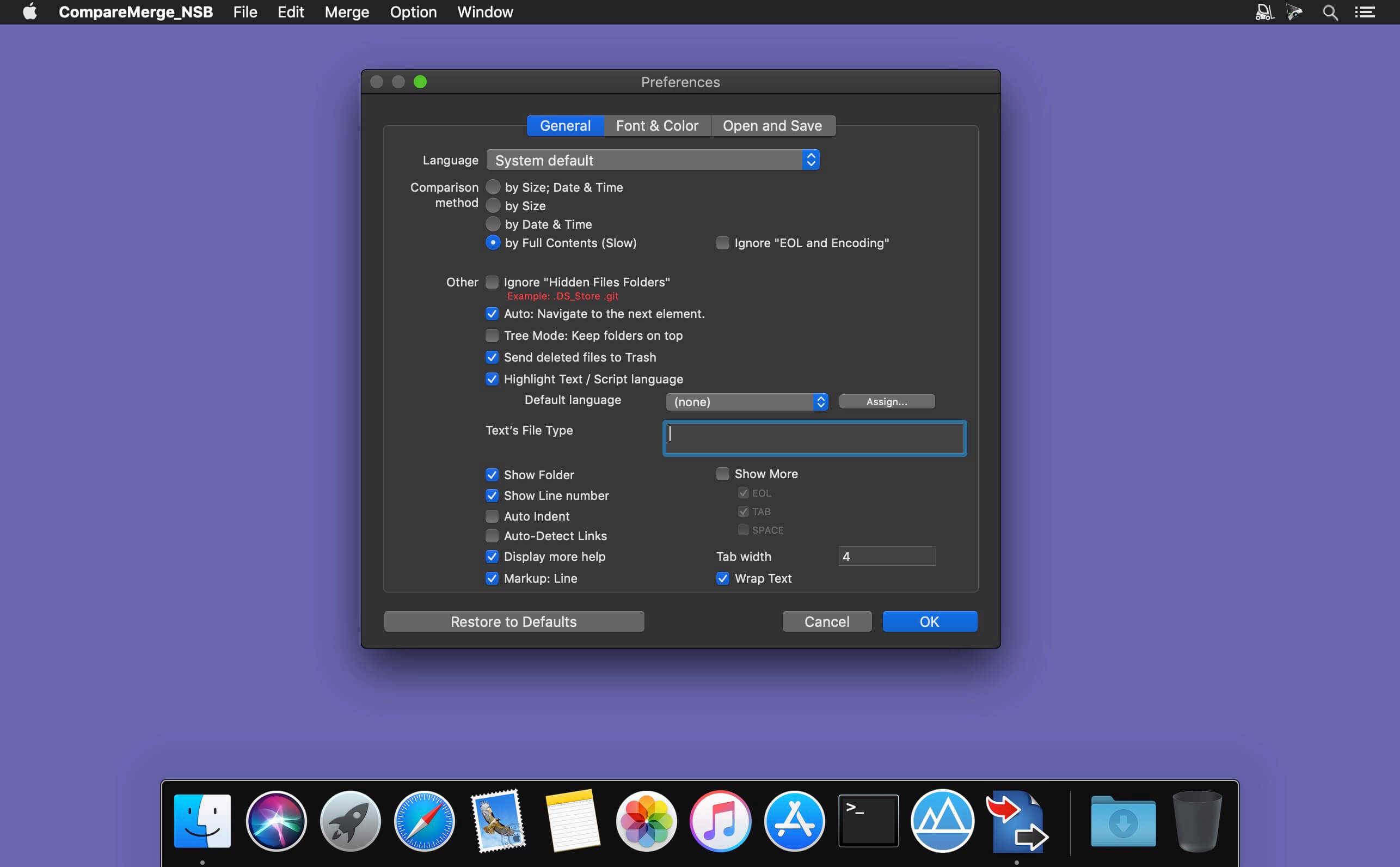

Beyond compare 3 tutorial download#

You should download a copy of the ZedBoard schematics to determine the constraints. We call this information constraints because it constrains the compiler– it can’t just pick one, but instead must use the one you constrain it to.Ĭreate an XDC constraints source file and call it top.xdc. Sure, it knows there is an input pin called switch and an output pin called led, but which pins do you want to use? There are hundreds to choose from.

Beyond compare 3 tutorial code#

The compiler cannot turn your Verilog code into a working FPGA however because you have not given it enough information. In effect, it simply creates a wire and connects led to switch. This statement just means that the output led is to change whenever the input switch changes.

The only thing else in the design is the assignment statement. These will correspond to input and output pins on the actual FPGA. We declare the module to have a single input called switch and a single output called led. But, given that this is the simplest FPGA in the world, that is not necessary. We will learn later that modules can instantiate other modules to create a hierarchical design. A module is just a container for part or all of your design. This declares a Verilog module called top. The design should have a single input called switch and a single output called led.Įdit the file so it looks like this module top ( You can use the wizard to add ports if you like when Vivado creates the file, or you can add them yourself using the text editor.

Create a new project in Vivado called tutorial1 and add a Verilog file called top.v. First, we will make the simplest possible FPGA.

0 kommentar(er)

0 kommentar(er)